The MCU (microprocessor) interface circuit consists of d pins (INH, SR, DO, MS), where 1NH selects low level under MCU control, SR is used as data input, DO is data output, data input Or each bit of the output is determined by the MS end of the clock.

The writing process under the control of the MCU: the command written to the language processor, the data is input from the SR terminal, and the 1NH terminal is kept low when the MS terminal is valid, and the SR terminal is caused when the MS terminal is lowered from the high level to the low level. The input is valid. The write command is a 4-bit instruction. JObit start address, 8-bit control word or 16-bit termination address, where the 1Obit start address corresponds to a 10-bit address counter.

Read process under MCU control: After the read command is sent to the language processor, the first byte data is obtained from the DO end, and in the case where the rising edge of the MS terminal is valid, the rising edge of each MS end will be read sequentially. data. The read command can be completed, into a read status register, a read extended address counter, or a read address counter.

Manual control and MCU control mode selection: After the FC9201 language processor is powered on, the system provides a reset signal on the RT side, and the system enters the manual control mode. If you want to switch to the MCU control mode, you can send the lNH terminal to a negative pulse. MCU control is maintained during the pulse. If the system is to be transferred from the MCU control mode to the person = I = control mode, then the RT terminal needs to input a negative pulse, and the INH terminal returns to the high level. After power-on, manual control is interchanged with MCU control. The state detection word of the MCU does not need to be repeatedly written.

External memory compression technology: In order to make better use of the limited DRAM space, the compression mode is first written to the MCS bit in the state control word, and the PD1 and PD2 bits can select the parameters of the compression space, and then trigger according to the language of the SEN1 and SEN2 bits. Level, output valid language and invalid language.

External memory capacity: The maximum capacity of a group of DRAMs is 4Mbit. If 64-level extended pulse output is used, 64-level has 64×4Mbit capacity. When the rate is 16kHz, the recording or playback time is more than 4 hours.

Low-pass filter cut-off frequency selection: The low-pass filter cut-off frequency waveform is 3.4 kHz when the state control word BW bit is 0, and 2.7 kHz when it is 1. In the case of manual control, the low-pass BW is 2.7 kHz at a rate of 16 kHz and 3.4 kHz at a rate of 32 kHz.

Rate selection; when the external clock frequency is 3.58MHz, the rate selection is either 16kHz or 32kHz. To adjust the rate again, you can change the external clock oscillation frequency. For example, when the external 5.5MHz clock is used, the rate of 16kHz originally selected is changed to 24kHz.

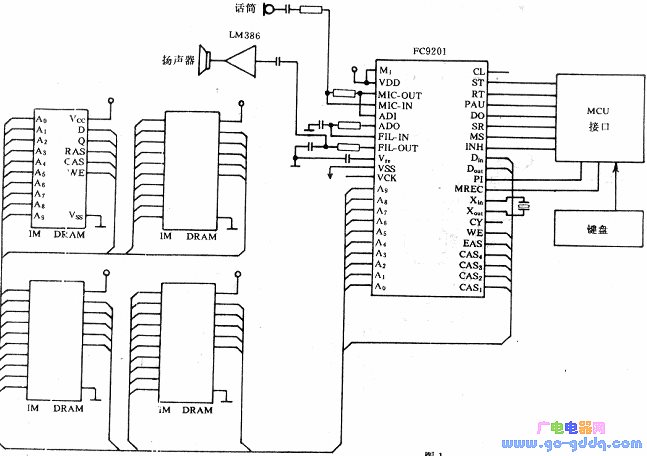

Application of FC9201: The figure above shows the electrical schematic of the typical application of FC9201.

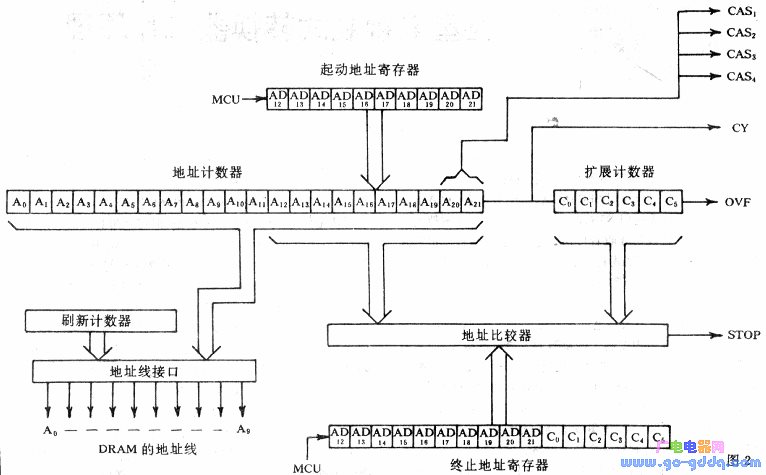

The circuit program is directly controlled by a microprocessor (ie, a single-chip microcomputer), and the 4-bit microcomputer interface (INH, SR, MS, DO end) is used for contact, recording or playback work can start, end address, state control word They are written into their respective status registers. The internal address assignment is shown in the figure below. The read status register, the address counter, and the extended counter register indicate the operation of the microprocessor. In this way, the microprocessor can be freely recorded or played back (for different DRAM regions).

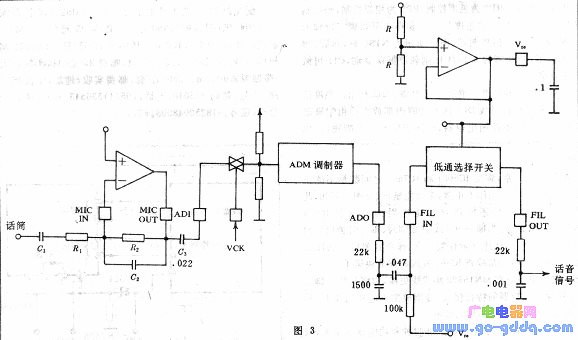

The analog signal part of the FC9201 includes microphone amplification, ADM filtered output, ADM modulation and demodulation, etc. (see the figure below). Microphone amplification is a Class I operational amplifier, its gain can be adjusted according to R2lRl, frequency characteristics can be adjusted R2, C2. The typical bandwidth is 3.4 kHz. The ADM input impedance is typically 25kΩ, and the coupling capacitor C3 can be selected based on a low frequency cutoff frequency of 300Hz to suppress 50 or 60Hz hum. In order to reduce the distortion of ADM modulation, the input signal amplitude of the ADI terminal should be within 2VP_P. The ADO signal, that is, the D/A conversion signal plus 1/2 VDD (Vre) level, is sent to the low-pass filter cut-off frequency selection switch, which is restored to the audio signal by the RC filtering of the FILOUT terminal, and is applied to the input end of the audio power amplifier. The speaker is sounded by the LM386 amplifier.

Disposable e-cigarettes,vape,eifbar

Nanning Nuoxin Technology Co., LTD , https://www.nx-vapes.com